Contents list available at Journal of e-Science Letters

# Journal of e-Science Letters

**Short Communication** | **ISSN**:3041-5454

# Low-Power VLSI Design for Next-Generation Devices

# Chaitanya Reddy Varala 🕒

VNR Vignana Jyothi Institute of Engineering and Technology, Hyderabad, Telangana, India

### **ABSTRACT**

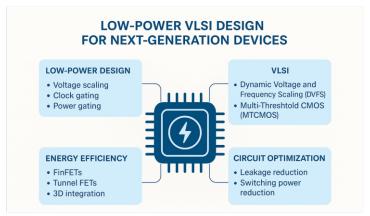

The evolution of modern electronics toward compact, high-performance, and energy-efficient systems has intensified the need for low-power Very-Large-Scale Integration (VLSI) design, particularly for next-generation devices such as wearable electronics, Internet of Things (IoT) nodes, biomedical implants, and mobile platforms. Low-power VLSI design addresses the challenges of reducing power consumption without compromising performance, area, and reliability. As device scaling approaches its physical limits, power dissipation due to leakage currents, dynamic switching, and short-circuit paths becomes a dominant concern, necessitating novel design methodologies and architectures. Techniques such as voltage scaling, clock gating, power gating, multi-threshold CMOS (MTCMOS), and dynamic voltage and frequency scaling (DVFS) are extensively researched and deployed to achieve optimal trade-offs. Moreover, emerging technologies like FinFETs, Tunnel FETs, and 3D integration are further enabling innovations in low-power architectures. By integrating advanced circuit-level strategies with algorithmic and architectural optimizations, low-power VLSI design is becoming pivotal in supporting the energy constraints and performance demands of future electronic systems, ensuring sustainable and scalable growth in the semiconductor industry.

$\textbf{\textit{Keywords:}} \ Low-power\ design, \textit{VLSI}, energy\ efficiency, next-generation\ devices, circuit\ optimization$

#### Introduction

The demand for high-performance yet energy-efficient electronic systems has surged with the proliferation of portable and embedded devices. From smartphones and tablets to smart wearables and IoT-enabled gadgets, modern applications require compact hardware that can deliver significant computational power while maintaining minimal power consumption. This requirement has driven intensive research and innovation in low-power VLSI (Very-Large-Scale Integration) design, which focuses on optimizing energy usage at the circuit, architecture, and system levels [1]. As technology nodes shrink and device complexity increases, the power consumption issue becomes even more critical, making lowpower design strategies indispensable for next-generation electronics [2]. Power dissipation in VLSI circuits typically comprises dynamic power, short-circuit power, and static (leakage) power. Dynamic power, which dominates in older technologies, results from charging and discharging capacitive loads during transistor switching. Short-circuit power arises momentarily when both PMOS and NMOS transistors conduct during switching transitions. Leakage power, negligible in older nodes, has become significant in deep-submicron technologies

**Citation:** Chaitanya Reddy Varala (2025). Low-Power VLSI Design for Next-Generation Devices. *Journal of e-Science Letters.* **DOI:** https://doi.org/10.51470/eSL.2025.6.1.22

Received: 30 January 2025 Revised: 25 February 2025 Accepted: 22 March 2025 Available: April 29 2025

Corresponding Authors: Chaitanya Reddy Varala

Email: vcr.0781@gmail.com

© 2025 by the authors. The license of Journal of e-Science Letters. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/)

due to reduced threshold voltages and thinner gate oxides. Therefore, modern low-power VLSI design must address all three components simultaneously through a combination of device-level and architectural techniques. One of the foundational strategies for power reduction is voltage scaling, which involves reducing the supply voltage to lower dynamic power consumption quadratically. However, this comes with a trade-off: lower supply voltages can lead to reduced noise margins and slower circuit operation [3]. To mitigate this, dynamic voltage and frequency scaling (DVFS) and multivoltage domains are used to dynamically adjust the performance and power trade-offs depending on the workload. Additionally, clock gating is employed to disable the clock signal to inactive parts of the circuit, significantly reducing unnecessary switching activity and dynamic power consumption. Another vital technique in low-power VLSI is the use of power gating, where inactive blocks of the chip are completely turned off by cutting off their power supply using sleep transistors. This approach effectively reduces leakage power during idle periods, especially in battery-operated devices that require long standby times. Coupled with architectural-level optimizations such as pipelining, parallelism, and cache reconfiguration, power gating allows designers to achieve higher energy efficiency without compromising system responsiveness. Recent advances in semiconductor technologies, such as FinFETs and fully depleted silicon-on-insulator (FD-SOI), have further enabled low-power operations by offering better control over short-channel effects and lower leakage. Additionally, the integration of non-volatile memory technologies, 3D ICs, and novel materials has opened new possibilities for energy-efficient computing [4]. These emerging technologies are critical in overcoming the limitations of traditional CMOS and scaling laws, ensuring that low-power design remains viable even as we approach sub-5nm technology nodes.

As low-power VLSI design continues to evolve, it is no longer confined to just hardware optimization. System-level co-design, incorporating both hardware and software, is now essential to maximize energy efficiency [5]. Techniques such as algorithm-aware hardware design, approximate computing, and machine learning-based power management have become mainstream. As the electronics industry moves toward ubiquitous computing and energy-harvesting applications, the significance of low-power VLSI design becomes increasingly central in shaping the next generation of smart, adaptive, and sustainable devices.

Fig 1. This Fig 1 illustrates the key components of low-power VLSI design for next-generation devices. At the center is a microchip representing the VLSI core, surrounded by four focus areas: Low-Power Design, VLSI Techniques, Energy Efficiency, and Circuit Optimization. Each section highlights critical strategies—such as voltage and clock gating, DVFS, FinFETs, and leakage reduction—that are essential for reducing power consumption while maintaining performance. This visual helps simplify the complex interplay of design approaches used to meet the stringent power and efficiency demands of modern electronics.

### 1. Voltage Scaling Techniques

Voltage scaling is one of the most effective strategies for reducing power consumption in VLSI circuits. Since dynamic power is directly proportional to the square of the supply voltage ( $P \propto V^2$ ), even a small reduction in voltage can result in significant energy savings. Designers often implement static voltage scaling (SVS) where the entire system operates at a reduced voltage, which helps in prolonging battery life in portable applications. However, SVS may compromise performance if not carefully managed. To address performance issues while still saving power, dynamic voltage scaling (DVS) and dynamic voltage and frequency scaling (DVFS) are employed. These techniques adjust the supply voltage and operating frequency on-the-fly based on the system's workload. During periods of low computational demand, the system lowers the voltage and frequency, thereby conserving energy. Conversely, it ramps up during performance-intensive tasks [6]. This adaptive control ensures an efficient balance between performance and power usage in modern devices.

### 2. Clock Gating

Clock gating is a widely used technique to minimize unnecessary switching activity in digital circuits. Since the clock signal drives most transitions in synchronous circuits, disabling the clock to idle blocks prevents power wastage from unwanted toggling. By integrating gating logic that enables or disables the clock based on control signals, designers can significantly reduce dynamic power. This technique is relatively simple to implement and compatible with existing design flows. While clock gating is beneficial, it must be carefully managed to avoid functional errors. Improper gating can lead to clock skew or race conditions, potentially causing data corruption. Therefore, synthesis tools and verification processes play a crucial role in ensuring correct implementation [7].

When used with other power reduction strategies, clock gating helps to achieve considerable savings in overall chip power consumption, especially in large-scale SoCs.

### 3. Power Gating

Power gating is an advanced technique that addresses static power consumption, particularly leakage currents. It involves shutting down power to unused logic blocks using sleep transistors, effectively disconnecting them from the power supply. This approach is especially useful in applications with long idle periods, such as mobile and wearable devices, where prolonged battery life is crucial. Implementing power gating poses several design challenges. The wake-up latency, ground bounce, and data retention during off periods need careful consideration. Techniques such as state-saving registers and isolation cells are often used to preserve critical data before powering down a block [8]. Despite these challenges, power gating remains a powerful solution for minimizing leakage power in deep submicron technologies.

### 4. Multi-Threshold CMOS (MTCMOS)

MTCMOS technology leverages transistors with different threshold voltages to balance power and performance. Low-threshold transistors are used in performance-critical paths to ensure speed, while high-threshold transistors are employed in non-critical paths to reduce leakage. This selective use of transistor types helps achieve optimal trade-offs between speed and power efficiency. The integration of MTCMOS requires additional design complexity, including careful path analysis and timing closure [9]. However, EDA tools now support automated threshold voltage assignment, making MTCMOS more accessible for commercial applications. This technology is particularly effective in ASICs and SoCs designed for low-power mobile and embedded systems.

### 5. Dynamic Voltage and Frequency Scaling (DVFS)

DVFS is a dynamic power management strategy that adjusts both the supply voltage and operating frequency of a processor based on workload demands. When performance requirements are low, reducing voltage and frequency helps conserve energy. During high-demand scenarios, voltage and frequency are increased to meet computational needs [10]. The success of DVFS depends heavily on system-level support, including software-based control algorithms and hardware sensors for workload monitoring. Thermal management units, operating system schedulers, and firmware all contribute to efficient DVFS implementation. It's widely used in processors for smartphones, laptops, and high-performance computing systems to balance performance with energy consumption.

### 6. FinFET Technology

FinFETs are three-dimensional transistors that offer superior control over the channel compared to traditional planar CMOS transistors. Their structure reduces leakage and improves switching speed, making them ideal for low-power VLSI designs. FinFETs also allow continued scaling below 10nm technology nodes, where traditional MOSFETs suffer from short-channel effects. Despite their advantages, FinFETs introduce fabrication complexity and increased cost [11]. The transition from planar to FinFET requires new design tools, modeling techniques, and manufacturing processes. However, their energy efficiency benefits outweigh these challenges, making FinFETs the standard in leading-edge semiconductor processes.

### 7. Sub-Threshold Operation

Sub-threshold design involves operating transistors below their threshold voltage, drastically reducing power consumption. Though this leads to slower operation due to reduced current drive, it is highly beneficial in ultra-low-power applications like biomedical sensors and IoT devices, where speed is less critical. Designing circuits to operate reliably in the sub-threshold region is challenging due to process variation, temperature sensitivity, and increased susceptibility to noise [12]. Careful sizing of transistors and robust design techniques are essential. Nevertheless, sub-threshold operation offers a compelling approach to achieving minimal power operation in energy-constrained environments.

### 8. Adaptive Body Biasing (ABB)

ABB adjusts the body voltage of transistors to control their threshold voltage dynamically. Forward body biasing decreases the threshold voltage for faster operation, while reverse body biasing increases it to reduce leakage. This technique allows real-time adaptation to process variations, temperature, and workload. ABB requires special fabrication processes that allow independent control of the transistor body terminal. It also necessitates additional circuits for bias generation and control. When implemented effectively, ABB enhances both performance and power efficiency, making it suitable for adaptive VLSI systems.

### 9. Leakage Power Reduction Techniques

Leakage power has become a dominant issue in nanoscale technologies, especially during standby periods. Techniques such as transistor stacking, input vector control, and dual-Vt (threshold voltage) assignment help mitigate leakage. Each method works by either turning off leakage paths or reducing the susceptibility of transistors to leakage currents [13]. Designers must consider trade-offs in area and performance when applying leakage reduction strategies. Advanced simulation tools are often used to identify the most powerhungry nodes and apply selective optimization. Leakage reduction is critical for prolonging battery life and maintaining thermal stability in compact devices.

### 10. Use of Non-Volatile Memory (NVM)

Incorporating NVM such as MRAM, ReRAM, or FeRAM into VLSI designs can reduce power by eliminating the need for continuous refresh, as required in traditional volatile memory like DRAM. NVM retains data without power, making it suitable for energy-efficient cache, configuration storage, and embedded systems [14]. Design challenges include endurance limits, write latency, and integration with existing CMOS technology. Hybrid memory architectures combining NVM and SRAM/DRAM offer a balance between performance and power. As NVM technologies mature, they will play an increasingly important role in low-power VLSI systems.

### 11. Approximate Computing

Approximate computing leverages the inherent tolerance of certain applications (like multimedia processing or machine learning) to computational errors. By allowing slight inaccuracies, circuits can be simplified, resulting in lower power consumption and smaller area [10]. Designing approximate units involves identifying non-critical paths or operations and applying reduced-precision or inexact logic. While this technique is not universally applicable, it can offer substantial power savings in specific domains. It represents a paradigm

shift in VLSI design by trading precision for efficiency.

### 12. Clock Tree Optimization

The clock network consumes a significant portion of dynamic power in synchronous circuits. Optimizing the clock tree—by reducing its capacitive load, using low-power buffers, and applying localized clock distribution—can yield substantial energy savings [4]. EDA tools offer automated solutions for clock tree synthesis, balancing skew, power, and area. Advanced methods like resonant clocking and asynchronous clock domains further enhance power efficiency. Clock tree optimization remains a fundamental aspect of low-power VLSI design.

### 13.3D Integration and Stacking

3D ICs involve stacking multiple layers of circuits vertically, connected through through-silicon vias (TSVs). This approach reduces interconnect lengths, improving performance and lowering power consumption due to reduced capacitance [2]. Thermal management, TSV reliability, and manufacturing complexity are major challenges in 3D integration. However, the benefits in terms of form factor, energy efficiency, and performance make it attractive for memory cubes, logic-memory integration, and advanced SoCs in next-generation systems.

### 14. Energy Harvesting Interfaces

Low-power VLSI circuits can be designed to interface with energy harvesting sources like solar cells, vibration-based generators, or thermoelectric devices. These interfaces require ultra-low-power operation and efficient power management units to capture and store intermittent energy. Designing VLSI circuits for such interfaces involves optimizing power conversion efficiency, startup circuits, and leakage control. Energy harvesting expands the application of VLSI into self-sustaining systems, ideal for remote sensors and wearable technology [8].

### 15. System-Level Power Management

Power management at the system level integrates hardware and software to optimize energy usage across components. Techniques include power-aware scheduling, workload migration, and power domains that allow selective activation of subsystems. Effective system-level power management requires coordination between firmware, operating systems, and hardware modules. With intelligent policies, the system can maintain optimal performance while reducing energy expenditure [9]. This holistic approach is essential for next-generation devices requiring adaptability and extended operation on limited power sources.

### Conclusion

Low-power VLSI design stands as a cornerstone in the evolution of next-generation electronic systems, enabling the integration of complex functionalities within compact and energy-efficient architectures. As the demand for portable, wearable, and IoTenabled devices continues to rise, minimizing power consumption without compromising performance has become a primary design objective. Traditional methods such as voltage scaling, clock gating, and multi-threshold CMOS, alongside advanced strategies like FinFETs and sub-threshold operation, form a comprehensive toolkit that engineers can employ to balance energy efficiency with speed, area, and reliability.

These methodologies not only address dynamic and static power challenges but also ensure that modern systems can meet stringent power budgets while remaining thermally stable.

Moreover, the landscape of VLSI design is rapidly transforming with the adoption of newer technologies like 3D integration, non-volatile memory, and energy harvesting systems. These innovations bring forth a paradigm shift in how power is managed and utilized, enabling the development of selfpowered and context-aware devices. System-level co-design, which merges hardware optimization with intelligent software control, allows for dynamic adaptation to varying workloads, environmental conditions, and user interactions. This synergy is vital in achieving ultra-low-power operation, especially in applications where battery life and thermal constraints are critical, such as biomedical implants, edge computing, and wearable health monitors, the future of low-power VLSI design lies in interdisciplinary collaboration, where material science, microarchitecture, machine learning, and embedded software converge to unlock new levels of energy efficiency and functionality. The challenges posed by continued device scaling, environmental concerns, and the push toward sustainability demand innovative thinking and robust design methodologies. As semiconductor technology progresses beyond conventional CMOS limits, the emphasis on power-aware computing will grow even stronger, solidifying low-power VLSI design as a fundamental pillar in the creation of intelligent, sustainable, and future-ready electronic systems.

### References

- Sharma, A., & Sohal, H. (2017). Considerations for ultralow-power VLSI design—A survey. *Journal of Nanoelectronics and Optoelectronics*, 12(1), 1-21.

- 2. Chandrakasan, A. P., Daly, D. C., Kwong, J., & Ramadass, Y. K. (2008, June). Next generation micro-power systems. In *2008 IEEE Symposium on VLSI Circuits* (pp. 2-5). IEEE.

- 3. De, V., & Borkar, S. (2000, March). Low power and high performance design challenges in future technologies. In *Proceedings of the 10th Great Lakes symposium on VLSI* (pp. 1-6).

- 4. De, V., & Borkar, S. (1999, August). Technology and design challenges for low power and high performance. In *Proceedings of the 1999 international symposium on Low power electronics and design* (pp. 163-168).

- Divyanshu, D., Kumar, R., Khan, D., Amara, S., & Massoud, Y. (2022). Physically unclonable function using GSHE driven SOT assisted p-MTJ for next generation hardware security applications. *IEEE Access*, 10, 93029-93038.

- 6. Leibson, S., & Mehta, N. (2013). Xilinx ultrascale: The next-generation architecture for your next-generation architecture. *Xilinx White Paper WP435*, 143.

- Mangla, A., Chalkiadaki, M. A., Fadhuile, F., Taris, T., Deval, Y., & Enz, C. C. (2013). Design methodology for ultra lowpower analog circuits using next generation BSIM6 MOSFET compact model. *Microelectronics journal*, 44(7), 570-575.

- 8. Garimella, S. V., Fleischer, A. S., Murthy, J. Y., Keshavarzi, A., Prasher, R., Patel, C., & Raad, P. E. (2008). Thermal challenges in next-generation electronic systems. *IEEE Transactions on Components and Packaging Technologies*, 31(4),801-815.

- 9. Kang, W., Ran, Y., Zhang, Y., Lv, W., & Zhao, W. (2017). Modeling and exploration of the voltage-controlled magnetic anisotropy effect for the next-generation low-power and high-speed MRAM applications. *IEEE Transactions on Nanotechnology*, 16(3), 387-395.

- 10. Rakowski, M., Meagher, C., Nummy, K., Aboketaf, A., Ayala, J., Bian, Y., ... & Pellerin, J. (2020, March). 45nm CMOS-silicon photonics monolithic technology (45CLO) for next-generation, low power and high speed optical interconnects. In *Optical Fiber Communication Conference* (pp. T3H-3). Optica Publishing Group.

- 11. Pannuto, P., Lee, Y., Kuo, Y. S., Foo, Z., Kempke, B., Kim, G., ... & Dutta, P. (2015). MBus: An ultra-low power interconnect bus for next generation nanopower systems. *ACM SIGARCH Computer Architecture News*, 43(3S), 629-641.

- 12. Alioto, M. (2012). Ultra-low power VLSI circuit design demystified and explained: A tutorial. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 59(1), 3-29.

- 13. Cao, W., Jiang, J., Kang, J., Sarkar, D., Liu, W., & Banerjee, K. (2015, December). Designing band-to-band tunneling field-effect transistors with 2D semiconductors for next-generation low-power VLSI. In *2015 IEEE International Electron Devices Meeting (IEDM)* (pp. 12-3). IEEE.

- 14. Wentzloff, D. D., Calhoun, B. H., Min, R., Wang, A., Ickes, N., & Chandrakasan, A. P. (2004, January). Design considerations for next generation wireless power-aware microsensor nodes. In *17th International Conference on VLSI Design. Proceedings*. (pp. 361-367). IEEE.

25. www.scienceletters.researchfloor.org